四川安路開發(fā)板FPGA開發(fā)板套件

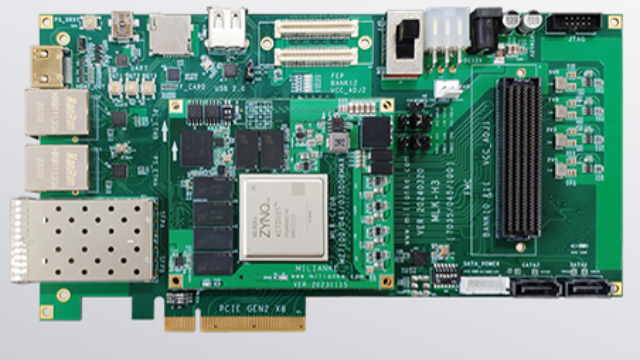

在通信領(lǐng)域,F(xiàn)PGA 開發(fā)板展現(xiàn)出的性能與適應(yīng)性。以 5G 通信基站的部分功能實(shí)現(xiàn)為例,基于 FPGA 開發(fā)板可以構(gòu)建的基帶處理單元。開發(fā)板利用其高速數(shù)據(jù)處理能力和靈活的邏輯資源,對(duì) 5G 信號(hào)進(jìn)行復(fù)雜的數(shù)字信號(hào)處理操作。在信道編碼環(huán)節(jié),能夠按照 5G 標(biāo)準(zhǔn)協(xié)議對(duì)數(shù)據(jù)進(jìn)行編碼,提高數(shù)據(jù)在無線信道傳輸中的可靠性;在調(diào)制解調(diào)過程中,準(zhǔn)確地將數(shù)字信號(hào)轉(zhuǎn)換為適合無線傳輸?shù)哪M信號(hào),并在接收端進(jìn)行反向操作,還原出原始數(shù)據(jù)。同時(shí),通過開發(fā)板上豐富的高速接口,如高速串行接口,可實(shí)現(xiàn)與其他基站設(shè)備網(wǎng)的高速數(shù)據(jù)傳輸,滿足 5G 通信對(duì)海量數(shù)據(jù)傳輸?shù)男枨蟆6遥捎?FPGA 開發(fā)板的可重構(gòu)特性,當(dāng)通信協(xié)議進(jìn)行升級(jí)或優(yōu)化時(shí),開發(fā)者能夠迅速對(duì)開發(fā)板上的邏輯功能進(jìn)行重新編程,使基站設(shè)備能夠適應(yīng)新的通信標(biāo)準(zhǔn),無需大規(guī)模更換硬件設(shè)備,降低了運(yùn)營(yíng)成本,提高了設(shè)備的使用壽命和適應(yīng)性,為 5G 通信網(wǎng)絡(luò)的穩(wěn)定運(yùn)行和持續(xù)發(fā)展提供了有力支持。若要進(jìn)行高速數(shù)據(jù)傳輸,帶有 SFP + 光纖接口、支持高速協(xié)議的 FPGA 開發(fā)板會(huì)是理想之選。四川安路開發(fā)板FPGA開發(fā)板套件

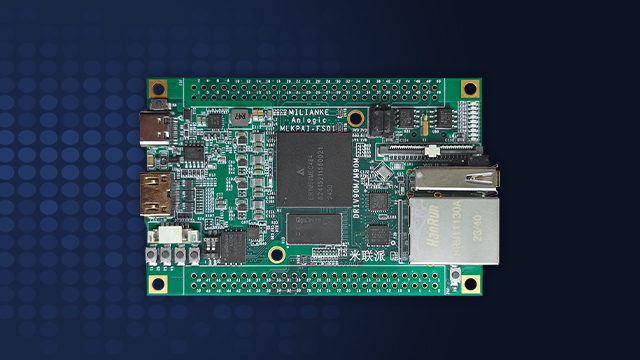

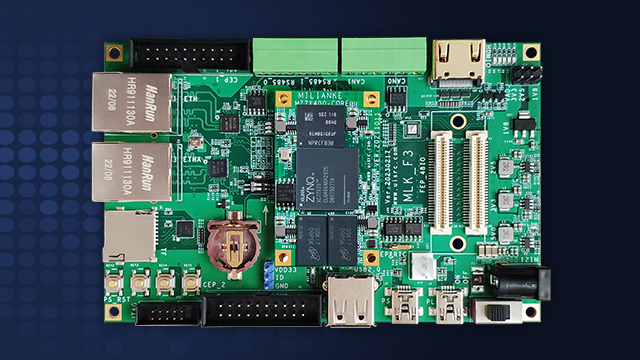

FPGA開發(fā)板作為硬件開發(fā)的重要平臺(tái),其硬件架構(gòu)精妙且復(fù)雜。以常見的XilinxArtix-7系列開發(fā)板為例,重要的FPGA芯片無疑是整個(gè)開發(fā)板的關(guān)鍵部件。像XC7A100T這類芯片,具備豐富的邏輯資源,擁有大量的邏輯單元,能實(shí)現(xiàn)各種復(fù)雜的數(shù)字邏輯電路,從簡(jiǎn)單的組合邏輯到復(fù)雜的時(shí)序邏輯均可勝任。在存儲(chǔ)資源方面,板載了不同類型的存儲(chǔ)器。例如,有用于高速數(shù)據(jù)緩存的SRAM,它能以極快的速度響應(yīng)數(shù)據(jù)的讀寫請(qǐng)求,為數(shù)據(jù)的處理提供支持;還有用于程序存儲(chǔ)的FLASH存儲(chǔ)器,可在斷電后依然保存已編寫的程序代碼,方便開發(fā)板在下次啟動(dòng)時(shí)直接調(diào)用。通信接口也是豐富多樣,具備以太網(wǎng)接口,能夠?qū)崿F(xiàn)開發(fā)板與外部網(wǎng)絡(luò)設(shè)備的高速數(shù)據(jù)交互,無論是進(jìn)行數(shù)據(jù)傳輸還是接入網(wǎng)絡(luò)系統(tǒng)都十分便捷;USB接口則方便連接各類外部設(shè)備,如電腦用于程序下載與調(diào)試,或者連接其他USB外設(shè)擴(kuò)展功能;此外,SPI、I2C等低速通信接口,可用于連接傳感器、EEPROM等低速外設(shè),擴(kuò)展開發(fā)板的功能范圍。這些硬件資源相互配合,為開發(fā)者提供了強(qiáng)大的開發(fā)基礎(chǔ),使得他們能夠在這個(gè)平臺(tái)上構(gòu)建出各種各樣滿足不同需求的硬件系統(tǒng)。 湖北工控板FPGA開發(fā)板工程師智能交通系統(tǒng)中,F(xiàn)PGA 開發(fā)板優(yōu)化交通流量監(jiān)測(cè)與信號(hào)燈控制。

FPGA開發(fā)板在教育領(lǐng)域扮演著越來越重要的角色,成為數(shù)字電路和嵌入式系統(tǒng)教學(xué)的重要工具。通過FPGA開發(fā)板,學(xué)生和學(xué)習(xí)者可以實(shí)踐性地理解數(shù)字邏輯設(shè)計(jì)的原理,掌握HDL編程的技巧,并加深對(duì)現(xiàn)代電子系統(tǒng)的理解。許多高校和培訓(xùn)機(jī)構(gòu)已經(jīng)將FPGA開發(fā)板納入課程體系,幫助學(xué)生提升實(shí)際操作能力和創(chuàng)新能力。此外,F(xiàn)PGA開發(fā)板的豐富資源和開源社區(qū)也為學(xué)習(xí)者提供了大量的教程和項(xiàng)目實(shí)例,進(jìn)一步降低了學(xué)習(xí)門檻,促進(jìn)了電子工程專業(yè)人才的培養(yǎng)。

FPGA開發(fā)板在醫(yī)療設(shè)備領(lǐng)域有著廣泛的應(yīng)用,為醫(yī)療技術(shù)的進(jìn)步貢獻(xiàn)力量。在醫(yī)學(xué)影像設(shè)備,如CT(計(jì)算機(jī)斷層掃描)和MRI(磁共振成像)設(shè)備中,開發(fā)板用于圖像數(shù)據(jù)的處理和重建。CT設(shè)備在掃描人體后,會(huì)產(chǎn)生大量的原始數(shù)據(jù),F(xiàn)PGA開發(fā)板能夠以高速并行處理的方式,對(duì)這些數(shù)據(jù)進(jìn)行運(yùn)算和處理,通過特定的算法將其重建為清晰的人體斷層圖像。在這個(gè)過程中,開發(fā)板的高速數(shù)據(jù)處理能力確保了圖像重建的速度,使得醫(yī)生能夠在短時(shí)間內(nèi)獲取患者的影像信息,提高診斷效率。在MRI設(shè)備中,開發(fā)板同樣發(fā)揮著關(guān)鍵作用,對(duì)磁共振信號(hào)進(jìn)行精確處理,增強(qiáng)圖像的分辨率和對(duì)比度,為醫(yī)生提供更準(zhǔn)確的診斷依據(jù)。此外,在一些便攜式醫(yī)療監(jiān)測(cè)設(shè)備中,F(xiàn)PGA開發(fā)板憑借其低功耗和靈活的特性,可對(duì)生理信號(hào),如心電、血壓、血氧等進(jìn)行實(shí)時(shí)采集、處理和分析,并通過無線通信模塊將數(shù)據(jù)傳輸至遠(yuǎn)程醫(yī)療平臺(tái),方便醫(yī)生對(duì)患者進(jìn)行遠(yuǎn)程監(jiān)護(hù)和診斷,為醫(yī)療服務(wù)的便捷性和及時(shí)性提供了技術(shù)保障。利用 FPGA 開發(fā)板的并行處理能力,能高效完成數(shù)字信號(hào)處理任務(wù)。

在數(shù)字信號(hào)處理領(lǐng)域,F(xiàn)PGA開發(fā)板憑借其強(qiáng)大的并行處理能力,展現(xiàn)出獨(dú)特的優(yōu)勢(shì)。以音頻信號(hào)處理為例,開發(fā)板可以同時(shí)處理多路音頻數(shù)據(jù)。在音頻編碼過程中,通過在FPGA上實(shí)現(xiàn)MP3、AAC等音頻編碼算法,將原始音頻信號(hào)壓縮為更小的數(shù)據(jù)量,便于存儲(chǔ)與傳輸。再將壓縮后的音頻數(shù)據(jù)還原為高質(zhì)量的音頻信號(hào)。對(duì)于復(fù)雜的音頻處理,如混響、回聲等,F(xiàn)PGA可以利用其豐富的邏輯資源,并行計(jì)算大量的音頻樣本數(shù)據(jù),生成相應(yīng)的效果。在視頻信號(hào)處理方面,開發(fā)板能夠?qū)Ω咔逡曨l流進(jìn)行實(shí)時(shí)處理,完成視頻的縮放、裁剪、濾波等操作。例如,在視頻監(jiān)控系統(tǒng)中,對(duì)攝像頭采集的視頻進(jìn)行預(yù)處理,增強(qiáng)畫面清晰度,為后續(xù)的圖像分析提供高質(zhì)量的數(shù)據(jù)源,滿足不同場(chǎng)景下對(duì)數(shù)字信號(hào)處理的多樣化需求。科研實(shí)驗(yàn)時(shí),F(xiàn)PGA 開發(fā)板為新技術(shù)驗(yàn)證與算法測(cè)試提供可靠硬件平臺(tái)。四川安路開發(fā)板FPGA開發(fā)板套件

學(xué)習(xí) FPGA 開發(fā)板,是掌握數(shù)字電路設(shè)計(jì)與硬件開發(fā)的重要途徑。四川安路開發(fā)板FPGA開發(fā)板套件

FPGA開發(fā)板的軟件生態(tài)同樣豐富,為開發(fā)者提供了的支持。在開發(fā)工具方面,Xilinx的Vivado軟件是一款功能強(qiáng)大且使用的開發(fā)套件。它集成了設(shè)計(jì)輸入、綜合、實(shí)現(xiàn)、仿真和調(diào)試等一系列功能。開發(fā)者可以通過硬件描述語言,如Verilog或VHDL,在Vivado中進(jìn)行設(shè)計(jì)輸入,將自己的電路設(shè)計(jì)思路轉(zhuǎn)化為代碼形式。綜合工具會(huì)將這些代碼轉(zhuǎn)化為門級(jí)網(wǎng)表,映射到FPGA芯片的邏輯資源上。實(shí)現(xiàn)過程則負(fù)責(zé)將網(wǎng)表布局到FPGA芯片的具置,并完成布線,確保信號(hào)能夠準(zhǔn)確傳輸。仿真功能允許開發(fā)者在實(shí)際硬件實(shí)現(xiàn)之前,對(duì)設(shè)計(jì)進(jìn)行功能驗(yàn)證,通過設(shè)置輸入激勵(lì),觀察輸出結(jié)果,檢查設(shè)計(jì)是否符合預(yù)期,降低了開發(fā)過程中的錯(cuò)誤風(fēng)險(xiǎn)。調(diào)試工具則在硬件實(shí)現(xiàn)后,幫助開發(fā)者定位和解決可能出現(xiàn)的問題,例如通過邏輯分析儀觀察內(nèi)部信號(hào)的變化,找出邏輯錯(cuò)誤或時(shí)序問題。同時(shí),Vivado還提供了豐富的IP核資源,開發(fā)者可以直接調(diào)用這些預(yù)先設(shè)計(jì)好的功能模塊,如數(shù)字信號(hào)處理模塊、通信協(xié)議模塊等,極大地縮短了開發(fā)周期,提高了開發(fā)效率,讓開發(fā)者能夠更專注于系統(tǒng)級(jí)的設(shè)計(jì)與創(chuàng)新。四川安路開發(fā)板FPGA開發(fā)板套件

- 天津開發(fā)板FPGA開發(fā)板特點(diǎn)與應(yīng)用 2025-06-19

- 福建FPGA定制項(xiàng)目教學(xué) 2025-06-19

- 福建工控板FPGA開發(fā)板工業(yè)模板 2025-06-19

- 定制FPGA定制項(xiàng)目教學(xué) 2025-06-19

- 河南FPGA開發(fā)板學(xué)習(xí)板 2025-06-19

- 陜西安路FPGA開發(fā)板工業(yè)模板 2025-06-19

- 天津賽靈思FPGA開發(fā)板平臺(tái) 2025-06-19

- 湖北入門級(jí)FPGA開發(fā)板編程 2025-06-19

- 湖南學(xué)習(xí)FPGA開發(fā)板教學(xué) 2025-06-19

- 浙江專注FPGA定制項(xiàng)目 2025-06-19

- 鄭州連續(xù)型量子隨機(jī)數(shù)發(fā)生器芯片使用方法 2025-06-19

- 揚(yáng)州陶瓷管陶瓷坩堝批發(fā) 2025-06-19

- 廣東零排放助焊劑技術(shù)支持 2025-06-19

- WINCOM萬代觸控感應(yīng)滾輪芯片批發(fā) 2025-06-19

- 天津開發(fā)板FPGA開發(fā)板特點(diǎn)與應(yīng)用 2025-06-19

- 山東LVDT壓力傳感器 2025-06-19

- 重慶矽鋼片硅鋼片批發(fā) 2025-06-19

- 靜安區(qū)特殊無線通信模塊解決方案廠家報(bào)價(jià) 2025-06-19

- 山東萬兆光模塊 2025-06-19

- 青海防靜電合成石生產(chǎn)廠家 2025-06-19